# A Fully Integrated Wireless Compressed Sensing Neural Signal Acquisition System for Chronic Recording and Brain Machine Interface

Xilin Liu, *Student Member, IEEE*, Milin Zhang, *Member, IEEE*, Tao Xiong, *Student Member, IEEE*, Andrew G. Richardson, *Member, IEEE*, Timothy H. Lucas, *Member, IEEE*, Peter S. Chin, *Member, IEEE*, Ralph Etienne-Cummings, *Fellow, IEEE*, Trac D. Tran, *Fellow, IEEE*, and Jan Van der Spiegel, *Fellow, IEEE*

Abstract—Reliable, multi-channel neural recording is critical to the neuroscience research and clinical treatment. However, most hardware development of fully integrated, multi-channel wireless neural recorders to-date, is still in the proof-of-concept stage. To be ready for practical use, the trade-offs between performance, power consumption, device size, robustness, and compatibility need to be carefully taken into account. This paper presents an optimized wireless compressed sensing neural signal recording system. The system takes advantages of both custom integrated circuits and universal compatible wireless solutions. The proposed system includes an implantable wireless system-on-chip (SoC) and an external wireless relay. The SoC integrates 16-channel low-noise neural amplifiers, programmable filters and gain stages, a SAR ADC, a real-time compressed sensing module, and a near field wireless power and data transmission link. The external relay integrates a 32 bit low-power microcontroller with Bluetooth 4.0 wireless module, a programming interface, and an inductive charging unit. The SoC achieves high signal recording quality with minimized power consumption, while reducing the risk of infection from through-skin connectors. The external relay maximizes the compatibility and programmability. The proposed compressed sensing module is highly configurable, featuring a SNDR of 9.78 dB with a compression ratio of  $8 \times$ . The SoC has been fabricated in a 180 nm standard CMOS technology, occupying 2.1 mm  $\times$  0.6 mm silicon area. A pre-implantable system has been assembled to demonstrate the proposed paradigm. The developed system has been successfully used for long-term wireless neural recording in freely behaving rhesus monkey.

*Index Terms*—Brain machine interface, compressed sensing, high energy efficiency, neural recording, wireless multi-channel recording.

Manuscript received October 7, 2015; revised December 24, 2015 and March 7, 2016; accepted April 2, 2016. Date of publication July 18, 2016; date of current version July 26, 2016. The work was done as part the National Science Foundation grant 1404041. This paper was recommended by Associate Editor A. Basu. (*Corresponding author: Milin Zhang.*)

X. Liu and J. Van der Spiegel are with the Department of Electrical and Systems Engineering (ESE), University of Pennsylvaniaa, Philadelphia, PA 19104 USA.

M. Zhang is with the Department of Electronic Engineering, Tsinghua University, Beijing 100084, China (e-mail: zhangmilin@gmail.com; zhangmilin@seas.upenn.edu).

T. Xiong, P. S. Chin, R. Etienne-Cummings, and T. D. Tran are with the Department of Electrical and Computer Engineering, Johns Hopkins University, Baltimore, MD 21218 USA.

A. G. Richardson and T. H. Lucas are with the Department of Neurosurgery, University of Pennsylvania, Philadelphia, PA 19104 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TBCAS.2016.2574362

## I. INTRODUCTION

**T**EURAL recording of large-scale brain activities revo-N lutionizes our understanding of the human brain [1]. Recent studies estimate that simultaneous invasive recording of 100 000 neurons are needed for decoding full-body movements [2], which is beyond the ability of the cutting-edge brain machine interface (BMI) devices. In practical neuroscience research, the multi-channel recording from a freely behaving animal in a natural environment is important for a wide range of experiments, however, most research to-date still relies on rack-mount equipments. The required recording of high bandwidth neural signals in multi-channels, multi-brain areas via wireless miniature devices places a big challenge on existing electronic technology and design techniques. The design optimizations of a fully integrated neural signal acquisition system with on-chip data compression is thus highly desirable.

There are several key requirements of a successful chronic invasive neural recording system: i) longevity requirement, safe electrode interface, minimum tissue damage and infection; ii) noise, bandwidth and channel count requirement for the target signal; iii) sufficient battery life to support long-term recording; and iv) reliable data storage or wireless transmission. In addition, the research of BMI usually requires the front-end to be highly programmable, wireless compatible with commercial equipments and sensors, and also easy to upgrade. All of these features together constitute a practical recording system for neuroscience research and BMI development. A balance between the requirements of each system blocks need to be carefully considered.

Many prior neural recording systems have been reported with improvements in noise performance, channel count, wireless communication, and system power consumption. For neural amplifier designs, low-noise amplifiers with closed-loop gain set by capacitors [3]–[7], and resistors [8], [9] have been commonly used. Chopping is usually adopted to achieve ultra low-noise in low frequency band [4], [5], [8]. Systems with large number of channels have also been reported [7], [10]–[12]. Several of these designs integrate a wireless transceiver. Among them, ISM band FSK [7], [13], [14], FM [15], [16], UWB [11], [17], and backscattering [10], [18], [19] are commonly used. In addition, some of the systems are fully integrated and potentially implantable [10], [12], [20].

1932-4545 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

On-chip data compression is an effective solution to reduce the system power by cutting off the data rate of the wireless telemetry, which is usually the power bottleneck of the overall system [21]. Various on-chip data compression techniques for neural signals have been proposed. For single or multi-units action potential recording, spike detection [22], and spike sorting [23] are the most effective ways to reduce the recording data rate, and can also be used to drive the BMIs directly. The hardware implementation of spike detection can be as simple as a comparator with a pre-defined threshold. A compression ratio higher than  $100 \times$  can be achieved with little power consumption [24]. However, this is usually at the price of losing information of the raw waveform, and can also be unreliable in long-time recording since the spike waveform may change due to the change of electrode impedance or electrode displacement. For EEG, ECoG, or LFP, wavelet transformation is an effective solution, given its high compression ratio and good reconstruction quality [25], [26]. However, the hardware implementation of wavelet transformation is nontrivial and usually takes considerable area and power. Moreover, a custom design for a specific signal type and sampling frequency significantly reduces the potential applications of the traditional recording compression systems.

Compressed sensing is an emerging signal processing technique that enables sub-Nyquist sampling and near lossless reconstruction of a signal [27]. Since it was introduced in 2006 [28], the compressed sensing technique has also been successfully applied to rapid MRI [28], computational image sensors [29], biomedical sensors [21], [30], high frequency receivers [31], and other applications. Compressed sensing is especially attractive to neural signal recording given its minimum hardware cost in the front-end, favouring power constrainted implanted devices. Prior research shows the sparsity of neural signals in different frequency bands [30], [32]–[34]. Since an on-chip transformation using random matrix usually achieves sufficient incoherence and restricted isometry property (RIP) [35], a general purpose recording device can be designed without the knowledge of the target signal.

In addition, the compressed sensing measurements can also be used in signal processing (e.g., machine learning classifiers) [36], or driving BMI directly. Without a full reconstruction of the raw signal, the processing in the compressed domain can be easily implemented in a low-power embedded systems.

In this paper, we describe a paradigm that meets the aforementioned requirements of a chronic neural recording system. The proposed system consists of an implantable wireless SoC and an external wearable transceiver sub-system. The system design realizes a trade-off between power consumption, compatibility, upgradability, without sacrificing the recorded signal quality. Compared with previous designs, this work presents a complete wireless system that is ready to use in neuroscience research and BMI applications. Long term recording in freely moving animals have been successfully conducted using the developed system prototypes. The system paradigm and circuit techniques proposed in this work can be used in many relevant neural recording devices' development.

The paper is organized as follows. Section II presents the overview of the proposed system. Section III shows the circuits

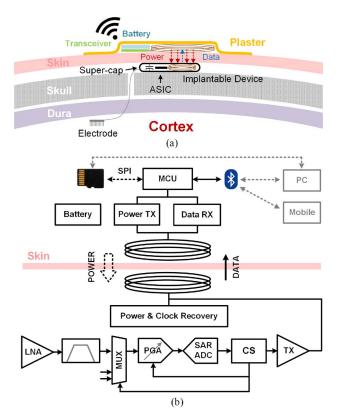

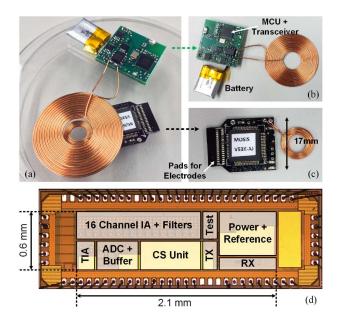

Fig. 1. (a) Illustration of the proposed chronic neural signal recording system using a fully integrated compressed sensing chip, and (b) the architecture of the chip.

implementation of each building blocks. Section IV shows the measurement results, while Section V concludes the paper.

# **II. NEURAL SIGNAL ACQUISITION SYSTEM OVERVIEW**

The paradigm of the chronic wireless neural signal acquisition system is illustrated in Fig. 1. The system has a dedicated implantable sub-system and a flexible external sub-system. The implantable sub-system contains a fully integrated compressed sensing neural signal recording SoC, an inductive coil and a super capacitor within a miniature bio-compatible package. The device can be placed under the skin but above the skull bone, while the recording electrode can be placed in any brain area of interest. The external sub-system consists of a standard wireless transceiver, a rechargeable battery, and a coil in a flexible substrate. The external sub-system powers the implanted device and collects data back through backscattering.

The advantages of the proposed system are three-folds: i) the implanted wireless device leaves the skin intact, which reduces the risk of infection, ii) the battery is left externally so that the device's life time will not be limited by the battery's recharging cycles, and the toxicity associated with batteries will not be a potential danger to the subject, iii) the external transceiver makes the system flexible and versatile, for instance, different wireless solutions or flash memory can be used for different situations. The upgrading of the system is also much easier, since the chronic implant can be used for years or even decades while the digital and wireless electronics develop much faster than the analog recording interface.

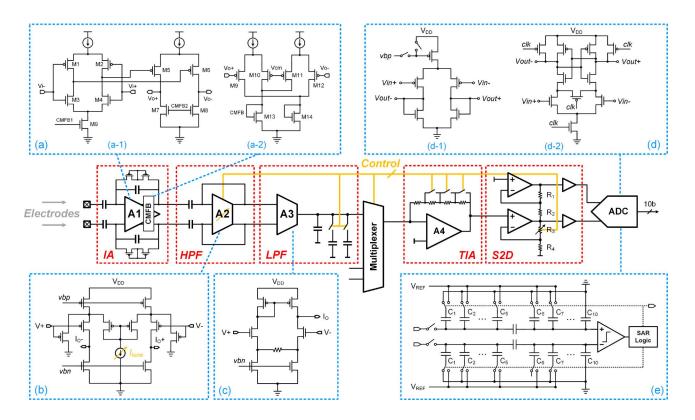

Fig. 2. Analog front-end of the proposed system. The signal chain includes signal amplification, filtering, voltage-to-current and current-to-voltage conversion in programmable cut-off frequency and gain. A 10-bit SAR ADC is used to digitize the signal.

A single pair of coils is used for both power delivery and data read back. A carrier frequency of 13.56 MHz is chosen given the trade-off between the power transfer efficiency and the data rate. Compressed sensing reduces the data rate of the wireless uplink, which is especially helpful in multiple channel recording.

#### **III. CIRCUITS IMPLEMENTATION**

# A. Energy Efficient Analog Front-End

Fig. 2 shows the block diagram of the analog front-end implemented in this work. A fully differential low-noise instrumentation amplifier (IA) is used to amplify the neural signal. A following gm-C based high pass filter stage (HPF) conditions the signal with a tunable cut-off frequency. The next stage (LFP) is an operational transconductance amplifier (OTA) that converts the voltage signal into current with programmable low-pass frequency corner. The current outputs from each channel are multiplexed and then converted to a voltage using a transimpedance amplifier (TIA) with a programable gain. A single-to-differential (S2D) converter is used to drive the differential input ADC with an additional programmable gain. A 10-bit SAR ADC digitizes the signal.

The IA in this work is a fully differential capacitor coupled neural amplifier, which amplifies the weak neural signal in a wide frequency band. The input capacitors block the large electrode offset and half-cell potential from the interface, giving a maximum input range. The closed-loop differential gain is set to be 34 dB to relieve the noise requirement for the following stages. The core of the IA is a low-noise OTA, as shown in Fig. 2(a-1). The OTA has been designed to maximize the noise and power efficiency. Two stages are used to provide sufficient open-loop gain. A complementary input stage (M1-M4) is used to increase the overall transconductance without increasing the quiescent current [37]. All of the input transistors are biased in the sub-threshold region to achieve a high energy efficiency. Since the complementary stage has a limited input range, a fully differential structure is chosen. The first stage dominates the noise, so the input referred noise of the OTA can be expressed as

$$\overline{v_{i,n,\text{tot}}^2} = \frac{1}{(g_{m1} + g_{m3})^2} \left[ 8KT\gamma(g_{m1} + g_{m3}) + 2\left(\frac{K_N g_{m3}}{C_{\text{ox},N} f W_N L_N} + \frac{K_P g_{m1}}{C_{\text{ox},P} f W_P L_P} \right) \right] \Delta f \quad (1)$$

where  $g_{m1}$  (=  $g_{m2}$ ) are the transconductance of M1 (M2), and  $g_{m3}$  (=  $g_{m4}$ ) are the transconductance of M3 (M4). The flicker noise can be reduced by increasing the widths and lengths of the input transistors. If only thermal noise is considered in the following design optimization, the input referred noise voltage equals to

$$\overline{V_{i,n,\text{rms}}} = \sqrt{\frac{8kT\gamma}{g_{m1} + g_{m3}}} \frac{\pi}{2} BW.$$

(2)

A biasing current of 1  $\mu$ A is used in the first stage as a tradeoff between power and noise. A biasing current of 20 nA is used in the second stage. The dominant pole is set at the second stage, and stability is guaranteed by adding an additional capacitive load. The complementary input amplifier suffers from sensitivity of PVT variations [38]. Common mode feedback, as shown in Fig. 2(a-2), is adopted to stabilize the DC output at half supply voltage.

An ultra low-power programmable bandpass filter is integrated in each channel for selecting the frequency band of interest. The first stage is a fully-differential Gm-C highpass filter. The circuit schematic of the Gm block is show as A2 in Fig. 2(b). Current division and local feedback are used to achieve low transconductance and an extended linear input range. The cut-off frequency can be programmed by tuning the transconductance. The second stage of the filter is a single-ended Gm-C based low pass filter. The circuit schematic of the Gm block is show as A3 in Fig. 2(c). Source degeneration is used to achieve high linearity. The differential voltage signal is converted into a single-end current signal. Since a standard current mirror load is used, no extra power is wasted for this conversion, but the single-ended operation reduces the capacitor array size by half, which is important for this design to be implemented at the channel level. The low-pass frequency can be programmed by selecting the load capacitors.

The single-ended current output of the 16 channel is selected by a multiplexer. The single-ended signal reduces the effort in routing, the current signal does not have R-I drop problem in long signal line, and it is less susceptible to noise. The following TIA is used to convert the current signal back to voltage with a programmable gain. The gain can be set to be  $5\times$ ,  $6\times$ ,  $7\times$ ,  $8\times$  by the compressed sensing digital processor. The gain of  $2\times$ ,  $4\times$ , can be easily achieved in the binary digital processor, and the  $3\times$  can be achieved from shifting the  $6\times$  signal by 1 bit.

A single-to-differential converter (S2D) is used to convert the single-ended voltage output from the TIA to differential voltages around the half supply voltage. Additional programmable gain is added in this stage. The resistor values are designed to be  $R_1 = R_2 = R_4$ , and the voltage gain is  $2(1 + R_3/R_4)$ .  $R_3$  can be programmed by a shift register. A Class-AB output stage has been designed to drive the sample-and-hold circuits of the following ADC stage.

A 10-bit successive approximation register (SAR) ADC is implemented for signal digitization. A SAR ADC is attractive for low-power, moderate resolution data conversion. Since a miniature unit capacitor can be used in a conventional binary capacitor array for the SAR ADC without compromising the ENOB, custom designed capacitors are often used to achieve low input capacitance and thus ultra low-power [39], [40]. However, these designs usually require custom characterization for a specific fabrication process. In this work, a split capacitor array is adopted to reduce the total capacitance, lowering the power consumption and area. The overall ADC architecture is shown in Fig. 2(e). The capacitors are realized as a standard metal-insulator-metal (MIM) structure. Monotonic switching procedure is applied to minimize the power con-

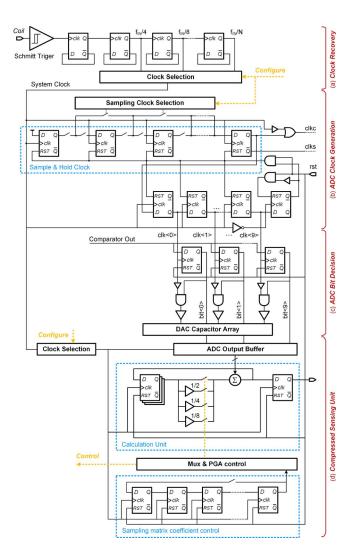

Fig. 3. Blocks and circuit schematics of the digital units. (a) Clock recovery and division module. (b) ADC clock generation circuits. (c) ADC bit decision and DAC control circuits. (d) Compressive sensing processing unit. A linear congruential pseudo random number generator is used to generate all the entries of the sampling matrix.

sumption from unnecessarily charging and discharging of the capacitor array [39]. In addition, in the monotonic switching procedure, the first comparison is performed without switching, and the total capacitance is the same as the conventional capacitive SAR ADC's DAC array. So we convert the single-ended signal to back to differential without penalty in die area and power consumption, but reduces the requirement for the comparator's design. A cascaded three-stage preamplifier with a dynamic latch is used as the comparator for the ADC. The schematics of the preamplifier and the latch are shown in Fig. 2(d).

The control logic generation circuitry is shown in Fig. 3(b). A global reset signal is used to synchronize the start of the AD conversion, and the control logic generation is cyclic. The clock cycle for the sample and hold time is configurable, and is used to compensate the processing time for the following compressed sensing stage for different configurations.

#### B. Compressed Sensing Module

Compressive sensing enables to sample signals at a rate lower than the Nyquist rate without greatly sacrificing the quality of the original signal. The digitized neural signal,  $x_{in}$ , of a single channel is fed into the digital processing unit

$$y = \Phi x_{\rm in} \tag{3}$$

that can be written as

$$\begin{bmatrix} y_0 \\ y_1 \\ \vdots \\ y_M \end{bmatrix} = \begin{bmatrix} \Phi_{11} & \Phi_{12} & \cdots & \Phi_{1N} \\ \Phi_{21} & \Phi_{22} & \cdots & \Phi_{2N} \\ \vdots & \vdots & \ddots & \vdots \\ \Phi_{M1} & \Phi_{M2} & \cdots & \Phi_{MN} \end{bmatrix} \begin{bmatrix} x_{in_0} \\ x_{in_1} \\ \vdots \\ x_{in_N} \end{bmatrix}.$$

(4)

Eq. (4) can be rewritten in the form of a summary of vector multiplications, as

$$\begin{bmatrix} y_0\\y_1\\\vdots\\y_M \end{bmatrix} = \sum_{i=1}^M \left( \begin{bmatrix} \Phi_{1i}\\\Phi_{2i}\\\vdots\\\Phi_{Mi} \end{bmatrix} x_{in_{i-1}} \right).$$

(5)

There are two modes of operation. In the simple mode, the entries of the sampling matrix  $\Phi$  are assigned to be 0, +1, or -1; in the high resolution mode, the entries can be assigned to be  $0, \pm (1/8), \pm (2/8), \ldots, \pm (7/8)$ . The compression ratio can be evaluated from M/N. In order to avoid large on-chip storage for the sampling matrix, a shift register chain is used to preload the coefficients at the beginning of each sampling loop. Fig. 3(d) illustrates the block diagram of the compressive sensing processing unit. Parallel output from the ADC is fed into the digital model. A simple sign control is applied before sending the ADC output to the adder for the simple mode. For the high resolution mode, the entry coefficients  $\pm(3/8), \pm(5/8)$  and  $\pm(7/8)$  are realized by configuring the gain of the analog amplifier to 3, 5, and 7, respectively, while shifting the ADC output by 3-bit before sending the ADC output to the adder. The entries coefficients  $\pm (1/8), \pm (2/8)$ and  $\pm(4/8)$  are realized by configuring the gain of the analog amplifier to 1 while shifting the ADC output by 3-bit, 2-bit, and 1-bit, respectively. The entries coefficients  $\pm (2/8)$  and  $\pm (6/8)$ are realized by configuring the gain of the analog amplifier to 1 and 3, respectively, while shifting the ADC output by 2-bit. There are M (M is equal to 16 in the proposed design) vector multiplication units integrated in the system. The entries of  $\Phi$  is randomly generated off-line and used for the logic control inside of each vector multiplication unit. The output measurement y is reset after every N iteration. N is tunable to meet different compression ratio requirement. The dimension of  $x_{in}$  is controlled by the iteration times. A parallel to serial convertor is integrated in the system for the readout of the measurements.

According to CS theory, a dictionary for sparsifying neural signals is required for sparse recovery. In this section, neural data recording without compression is performed to generate

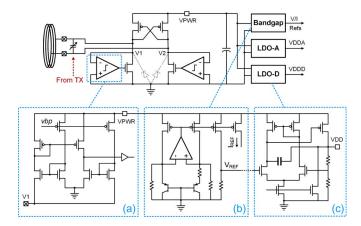

Fig. 4. Inductive power management module, including active rectifier and LDOs for analog and digital power supplies. (a) Circuit schematic of the comparator. (b) Bandgap reference. (c) LDO (start-up circuits are not shown).

a database for algorithm analysis at the very beginning. The database is divided into two halves, where one half is used for training the signal dependent dictionary **D** by unsupervised dictionary learning algorithm [33] and another half is used for testing the recovery performance. In proposed CS framework, we adopt on-chip Bernoulli sensing matrix  $\Phi$  to compress the neural spikes or LFP **x** of length N into measurements y of length M, where normally  $M \ll N$  and compression ratio is defined by M/N. The recovery problem below can be solved by Orthogonal Matching Pursuit [41]

$$\min_{\mathbf{a}} \|\mathbf{y} - \mathbf{\Phi} \mathbf{D} \mathbf{a}\|_2^2 \quad \text{s.t. } \|\mathbf{a}\|_0 \le S$$

where **a** is the sparse coefficient vector and S indicates the sparse level, which ranges from 2 to 10. The recovered signal is defined as  $\hat{\mathbf{x}} = \mathbf{D}\mathbf{a}$  and the recovery quality is quantitatively evaluated by signal-to-noise and distortion ratio (SNDR) which is found by [42]

$$SNDR = 20 \times \log \frac{\|\mathbf{x}\|_2}{\|\mathbf{x} - \hat{\mathbf{x}}\|_2}.$$

## C. On-Chip Wireless Power and Data Link

A low-power backscatter based wireless transmitter communicates with the external transceiver [43]. The backscatter transmitter consists of a PWM encoder and buffered transistor for antenna impedance modulation.

An active rectifier is used to achieve higher power efficiency [44]. Coupling coils are implemented off-chip. The system clock is recovered from the power waveform [16]. The circuitry of the clock recovery and division module is shown in Fig. 3(a). The clock frequency can be configured by the register. Standard bandgap reference and low drop-out (LDO) are used in the power management unit. The block diagram and the circuit schematics of the power management module are shown in Fig. 4.

| CIIII STECIFICATIONS SUMMART |                 |                         |                      |  |  |  |  |  |

|------------------------------|-----------------|-------------------------|----------------------|--|--|--|--|--|

| Neural Amplifier             |                 | CS Processor            |                      |  |  |  |  |  |

| Midband Gain                 | 34.1dB          | Input Channel           | up to 16             |  |  |  |  |  |

| Bandwidth                    | 0.5Hz - 7kHz    | CS Ratio                | up to 8x             |  |  |  |  |  |

| LNA Noise                    | $2.85 \mu$ Vrms | Clock freq.             | 4MHz                 |  |  |  |  |  |

| THD (1mV)                    | -63 dB          | Wireless Power and Data |                      |  |  |  |  |  |

| NEF/PEF                      | 1.58/4.5        | Carrier freq.           | 13.56 MHz            |  |  |  |  |  |

| CMRR                         | >80dB           | Power efficiency        | up to 73%            |  |  |  |  |  |

| PSRR                         | >67dB           | Distance                | up to 10mm           |  |  |  |  |  |

| SAR ADC                      |                 | Power                   |                      |  |  |  |  |  |

| ENOB                         | 9.1             | Analog Front-end        | $2.5\mu W$ (per ch.) |  |  |  |  |  |

| Sampling Rate                | 1MSps           | ADC                     | $35\mu$ W(@1MSps)    |  |  |  |  |  |

| INL (LSB)                    | +0.62/-0.85     | CS Processor            | $77\mu W$            |  |  |  |  |  |

| DNL (LSB)                    | +0.69/-0.92     | TX transmitter          | $27\mu W$            |  |  |  |  |  |

| FoM(fJ/step)                 | 34.2            | Total (avg.)            | 254µW                |  |  |  |  |  |

TABLE I Chip Specifications Summary

# D. External Wireless Relay Board

An external wireless relay board has also been designed to demonstrate the proposed paradigm. The external sub-system consists of a microcontroller with integrated wireless transceiver, envelop detection circuits for reading the backscattered signal, power transmitter circuits, and battery management system.

A 32-bit ARM Cortex-M0 based wireless transceiver (Nordic Semiconductor nRF51822) is used as the central processor and wireless transceiver. The unit features 2.4 GHz transceiver, and supports Bluetooth 4.0 low-energy protocol, which provides an easy interface to the computer or mobile devices. A reliable wireless communication up to 5 m was measured in normal in-door environment. A Serial Peripheral Interface (SPI) based microSD card interface is optional in the system to allow long-term wireless recording without limited receiver range.

A computer user interface has been developed in Matlab to configure the device and read back the data. Signal reconduction and off-line analysis are also performed in the user interface.

# **IV. EXPERIMENTAL RESULTS**

The proposed SoC design has been fabricated in an IBM 180 nm standard CMOS technology, occupying a silicon area of 2.1 mm  $\times$  0.8 mm.

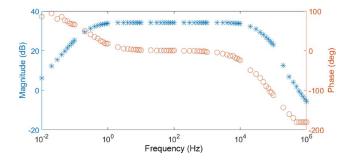

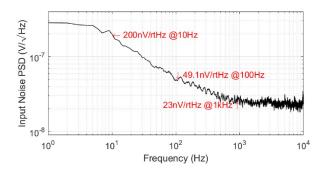

Bench testing was conducted to verify the functions of the chip and the system. The measured performance of the chip is summarized in Table I. The measured frequency response of the low noise amplifier is shown in Fig. 5. The input-referred noise spectrum is shown in Fig. 6. A rms noise floor of 2.8  $\mu$ V was measured. The measured CMRR and PSRR of the analog frontend in the frequency range of 0.5 Hz to 7 kHz are > 80 dB, and > 67 dB, respectively.

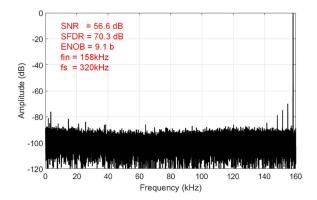

The SAR ADC's output spectrum with a near Nyquist input tone is shown in Fig. 7. The measured INL and DNL are 0.85 LSB and 0.92 LSB, respectively. The ADC achieves a SNR of 56.6 dB and a SFDR of 70.3 dB.

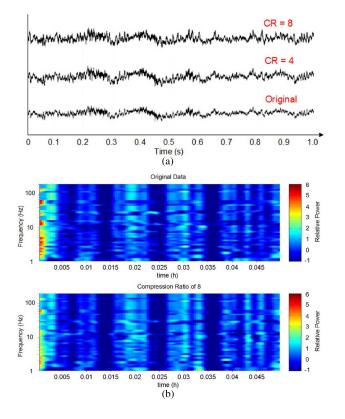

An invasive neural recording was performed in an anesthetized rat with a tungsten microelectrode placed in its motor cortex. Action potential data is extracted by configuring the filter with a passband of 300 Hz to 7 kHz. Different compression ratios from 2, to 4, to 8, and to 16 have been applied,

Fig. 5. Measured frequency response of the low noise amplifier (without filtering stages).

Fig. 6. Measured input-referred voltage noise spectrum.

Fig. 7. Measured FFT spectrum at 320 kS/s with a input tone of 158 kHz.

respectively. Dual-threshold level crossing spike detection has been used for both the uncompressed data and the restored data. Signal-to-noise distortion ratios (SNDR) of 3.60 dB, 9.78 dB, 30.60 dB, and 52.99 dB are achieved for compression ratios 16, 8, 4 and 2, respectively. Near lossless spike detection can be achieved while a lower than 8 compression ratio is applied.

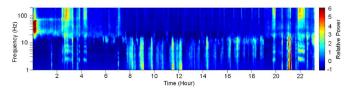

Fig. 8 compares both the time-domain waveform and the spectrogram of the uncompressed and restored local field potential (LFP) sampling data sets. The LFP exhibited rhythmic bouts of broadband power interleaved with low power epochs. According to Fig. 8(b), the time-frequency content of the restored signal was very similar to the uncompressed LFP. Signal-to-noise distortion ratio (SNDR) of 9.04 dB, 4.85 dB, and 3.78 dB are achieved for compression ratios 4, 8, and 16, respectively.

Fig. 8. (a) Comparison between the uncompressed sampling results and data restored from different compression ratio (CR). (b) Comparison on the spectrogram between uncompressed sampling results and data restored with a compression ratio (CR) of 8.

Fig. 9. Photography of an assembled demonstration system. (a) Power and data transmission testing setup across 5 mm plastic cap. (b) External transceiver board. (c) Implantable board. (d) The die photograph of the fabricated SoC.

A demonstration system was developed to show the proposed concept, as shown in Fig. 9. A open cavity plastic package is used for the chip, thus the size of the demonstration

Fig. 10. A 24-hour continuous recording in the hippocampus of a rhesus macaque during freely behavior.

implantable system is limited by the package. An additional ceramic capacitor is used to improve impedance matching. Two LEDs are used only for debugging. A couple of programming and debugging pads are left (not shown). No other off-chip components are required.

In-vivo evaluation of the device for long term operation was conducted in a rhesus macaque. An electrode was chronically implanted in the hippocampus. The recording device, including external transceiver, was housed in a small chamber that was fixed to the skull. Fig. 10 shows the spectrogram of a 24-hour continuous recording while the monkey was freely behaving in his home cage. The recording shows the states of hippocampal activity throughout the day. Greater power at higher frequencies (> 20 Hz) was associated with periods in which the animal was awake and freely moving about his home cage (hours 0-7.5 and 19-24). Greater power at low frequencies (< 20 Hz) was associated with sleeping (hours 7.5–19). Individual sleep cycles can be seen. Some broadband chewing artifacts were also present (around hours 3-4.5 and 20-22) corresponding with the times when the animal was fed. The overall activity pattern matches previous observations of sleepwake changes in neural activity.

#### V. CONCLUSION

In this work, a fully integrated wireless neural signal acquisition system is presented. A high efficiency wireless neural signal recording SoC with integrated compressed sensing processor was designed and fabricated in 180 nm CMOS technology. An external wireless relay was used to power the implantabe SoC, read back the data through backscattering, and transmit the data through universal wireless link. The system features high energy efficiency, high flexibility, compatibility, upgradability without compromising signal recording quality. By performing on-chip compressive sampling, the data rate is significantly reduced, which allows the system to support more recording channels without power penalty. According to the experimental results, a compression ratio up to  $8 \times$  will cause negligible reduction of the data quality and/or information available in the raw data. Table II compares the proposed design with previous works in literature. A pre-implant system was assembled and successfully demonstrated the proposed paradigm. Bench tests and In-vivo experimental results are presented. The system shows a promising chronic neural signal recording paradigm for neuroscience research and BMI applications.

| COMPARISON WITH STATE-OF-THE-ART WORKS |                    |                |                   |               |                 |                   |  |  |

|----------------------------------------|--------------------|----------------|-------------------|---------------|-----------------|-------------------|--|--|

| Reference                              | Deepu [45]         | Shoaran [46]   | Gangopadhyay [47] | Zhang [48]    | Biederman [49]  | This work         |  |  |

| Publication                            | 2014 JSSC          | 2014 TBioCAS   | 2014 JSSC         | 2015 JNE      | 2015 JSSC       | -                 |  |  |

| CMOS technology                        | 0.35um             | 180nm          | 130nm             | 180nm         | 65nm            | 180nm             |  |  |

| No. of channels                        | 4                  | 16             | 64                | 4             | 64              | 16                |  |  |

| Signal type                            | ECG                | EEG            | ECG               | Extracellular | Extracellular   | LFP/Extracellular |  |  |

| Input referred noise                   | 1.46uV             | 3.2uV          | <2uV              | 3.1uV         | 7.5uV           | 2.8uV             |  |  |

| Sampling rate/ch                       | 256/512Hz          | 4kHz           | 2kHz              | 20kHz         | 20kHz           | 20kHz             |  |  |

| Front-end NEF/PEF                      | 3.31/26.3          | 4.12/20.4      | -                 | -             | 3.6/12.9        | 1.58/4.5          |  |  |

| ADC ENOB                               | 9.3                | 9.2            | 6.5               | -             | 8.2             | 9.1               |  |  |

| AFE+ADC power/ch                       | 0.54uW (512Hz)     | >9.4uW (4kSps) | 28nW (2kSps)      | 15uW (20kSps) | 1.84uW (20kSps) | 3.2uW(20kSps)     |  |  |

| Compression method                     | Lin slope predict. | CS             | CS                | CS            | Spike Dect.     | CS                |  |  |

| Compression ratio                      | 2.55x              | up to 16x      | up to 6x          | 8x - 16x      | 8.3x (epochs)   | 8x - 16x          |  |  |

| Reconstruction SNR                     | -                  | >10dB (4x)     | -                 | <9dB (16x)    | -               | 9.78dB (8x)       |  |  |

| Wireless                               | -                  | -              | -                 | -             | -               | Backscattering    |  |  |

| In-vivo experiment                     | Yes                | -              | -                 | Yes           | Yes             | Yes               |  |  |

| System integration                     | -                  | -              | -                 | -             | Complete        | Complete          |  |  |

TABLE II Comparison With State-of-the-Art Works

#### ACKNOWLEDGMENT

The authors would like to thank the MOSIS Education Program for fabricating the chip.

#### REFERENCES

- [1] Human Brain Project Framework Partnership Agreement Proposal, 2014.

- [2] D. A. Schwarz, M. A. Lebedev, T. L. Hanson, D. F. Dimitrov, G. Lehew, J. Meloy, S. Rajangam, V. Subramanian, P. J. Ifft, Z. Li, A. Ramakrishnan, A. Tate, K. Z. Zhuang, and M. A. L. Nicolelis, "Chronic, wireless recordings of large-scale brain activity in freely moving rhesus monkeys," *Nat. Methods*, vol. 11, no. 6, pp. 670–676, 2014.

- [3] R. Harrison *et al.*, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, 2003.

- [4] T. Denison, K. Consoer, W. Santa, A. Avestruz, J. Cooley, and A. Kelly, "A 2 uW 100 nV/rtHz chopper-stabilized instrumentation amplifier for chronic measurement of neural field potentials," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2934–2945, 2007.

- [5] Q. Fan *et al.*, "A 1.8  $\mu$ W 60 nV/rtHz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1534–1543, 2011.

- [6] W. Wattanapanitch, M. Fee, and R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 2, pp. 136–47, Jun. 2007.

- [7] R. Harrison and P. Watkins, "A low-power integrated circuit for a wireless 100-electrode neural recording system," *IEEE J. Solid-State Circuits*, vol. 42, no. 1, pp. 123–133, Jan. 2007.

- [8] R. Yazicioglu and P. Merken, "A 60 mu W 60 nV/root Hz readout frontend for portable biopotential acquisition systems," *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 1100–1110, 2007.

- [9] N. Van Helleputte, S. Kim, H. Kim, J. P. Kim, C. Van Hoof, and R. F. Yazicioglu, "A 160 uA biopotential acquisition IC with fully integrated IA and motion artifact suppression," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 6, pp. 552–61, Dec. 2012.

- [10] R. Muller, H.-P. Le, W. Li, P. Ledochowitsch, S. Gambini, T. Bjorninen, and J. M. Rabaey, "A minimally invasive 64-channel wireless uECoG implant," *IEEE J. Solid-State Circuits*, vol. 50, no. 1, pp. 344–359, Apr. 2015.

- [11] M. S. Chae, Z. Yang, M. R. Yuce, L. Hoang, and W. Liu, "A 128-channel 6 mW wireless neural recording IC with spike feature extraction and UWB transmitter," *IEEE Trans. Neural Syst. Rehab. Eng.*, vol. 17, no. 4, pp. 312–21, Aug. 2009.

- [12] X. Zou, L. Liu, J. Cheong, and L. Yao, "A 100-channel 1-mW implantable neural recording IC," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 10, pp. 2584–2596, Oct. 2013.

- [13] R. R. Harrison, R. J. Kier, S. Member, C. A. Chestek, S. Member, V. Gilja, and I. Terms, "Wireless neural recording with single low-power integrated circuit," *IEEE Trans. Neural Syst. Rehab. Eng.*, vol. 17, no. 4, pp. 322–329, Aug. 2009.

- [14] A. Borna and K. Najafi, "A low power light weight wireless multichannel microsystem for reliable neural recording," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 439–451, Feb. 2014.

- [15] P. Mohseni, K. Najafi, S. J. Eliades, and X. Wang, "Wireless multichannel biopotential recording using an integrated FM telemetry circuit," *IEEE Trans. Neural Syst. Rehab. Eng.*, vol. 13, no. 3, pp. 263–271, Sep. 2005.

- [16] N. M. Neihart and R. R. Harrison, "Micropower circuits for bidirectional wireless telemetry in neural recording applications," *IEEE Trans. Biomed. Eng.*, vol. 52, no. 11, pp. 1950–1959, Nov. 2005.

- [17] H. Miranda, V. Gilja, C. A. Chestek, K. V. Shenoy, and T. H. Meng, "HermesD: A high-rate long-range wireless transmission system for simultaneous multichannel neural recording applications," *IEEE Trans. Biomed. Circuits Syst.*, vol. 4, no. 3, pp. 181–191, Jun. 2010.

- [18] W. Biederman and D. Yeager, "A fully-integrated, miniaturized (0.125 mm2) 10.5 uW wireless neural sensor," *IEEE J. Solid-State Circuits*, vol. 48, no. 4, pp. 960–970, Apr. 2013.

- [19] D. J. Yeager, J. Holleman, R. Prasad, J. R. Smith, and B. P. Otis, "Neural-WISP: A wirelessly powered neural interface with 1-m range," *IEEE Trans. Biomed. Circuits Syst.*, vol. 3, no. 6, pp. 379–387, Dec. 2009.

- [20] R. Olsson and K. Wise, "A three-dimensional neural recording microsystem with implantable data compression circuitry," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2796–2804, Dec. 2005.

- [21] F. Chen, A. P. Chandrakasan, and V. M. Stojanovi, "Design and Analysis of a Hardware-Efficient Compressed Sensing Architecture for Data Compression in Wireless Sensors," *IEEE J. Solid-State Circuits*, vol. 47, no. 3, pp. 744–756, 2012.

- [22] B. Gosselin and M. Sawan, "An ultra low-power CMOS automatic action potential detector," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 17, no. 4, pp. 346–353, Aug. 2009.

- [23] S. Narasimhan, H. J. Chiel, and S. Bhunia, "Ultra-low-power and robust digital-signal-processing hardware for implantable neural interface microsystems," *IEEE Trans. Biomed. Circuits Syst.*, vol. 5, no. 2, pp. 169–78, Apr. 2011.

- [24] X. Liu, M. Zhang, B. Subei, A. G. Richardson, T. H. Lucas, and J. Van Der Spiegel, "The PennBMBI: Design of a General Purpose Wireless Brain-Machine-Brain Interface System," *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 2, pp. 248–258, 2015.

- [25] K. G. Oweiss, A. Mason, Y. Suhail, A. M. Kamboh, and K. E. Thomson, "A scalable wavelet transform VLSI architecture for real-time signal processing in high-density intra-cortical implants," in *IEEE Trans. Circuits Sys. I, Reg. Papers*, vol. 54, no. 6, pp. 1266–1278, Jun. 2007.

- [26] Y. Yang, A. M. Kamboh, and A. J. Mason, "A configurable realtime DWTbased neural data compression and communication VLSI system for wireless implants," *J. Neurosci. Methods*, vol. 227, pp. 140–50, Apr. 2014.

- [27] E. J. Candes and M. B. Wakin, "An introduction to compressive sampling," *IEEE Signal Process. Mag.*, vol. 25, no. 2, pp. 21–30, Mar. 2008.

- [28] D. L. Donoho, "Compressed sensing," *IEEE Trans. Inf. Theory*, vol. 52, no. 4, pp. 1289–1306, Apr. 2006.

- [29] Y. Oike and A. El Gamal, "CMOS image sensor with per-column sigmadelta adc and programmable compressed sensing," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 318–328, 2013.

- [30] J. Zhang et al., "An efficient and compact compressed sensing microsystem for implantable neural recordings," *IEEE Trans. Biomed. Circuits* Syst., vol. 8, no. 4, pp. 485–496, 2014.

- [31] X. Chen, Z. Yu, and S. Hoyos, "A sub-Nyquist rate sampling receiver exploiting compressive sensing," *IEEE Trans. Circuits Syst. I, Reg. Papers*, pp. 507–520, 2011.

- [32] T. Xiong, J. Zhang, Y. Suo, D. N. Tran, R. Etienne-Cummings, S. Chin, and T. D. Tran, "A dictionary learning algorithm for multi-channel neural recordings," in *Proc. IEEE Biomed. Circuits Syst. Conf.*, 2014, pp. 9–12.

- [33] T. Xiong, J. Zhang, Y. Suo, D. N. Tran, R. Etienne-Cummings, S. Chin, and T. D. Tran, "An unsupervised dictionary learning algorithm for neural recordings," in *Proc. IEEE Int. Symp. Circuits Syst*, 2015, pp. 1010–1013.

- [34] S. Aviyente, "Compressed sensing framework for EEG compression," *Stat. Signal Process. IEEE*, pp. 181–184, 2007.

- [35] R. Baraniuk, "Compressive sensing," *IEEE Signal Process. Mag.*, vol. 24, no. 4, pp. 118–121, Jul. 2007.

- [36] M. Shoaib, N. K. Jha, and N. Verma, "Signal processing with direct computations on compressively sensed data," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 23, no. 1, pp. 30–43, Jan. 2015.

- [37] X. Liu, H. Zhu, M. Zhang, A. G. Richardson, T. H. Lucas, and J. Van Der Spiegel, "Design of a low-noise, high power efficiency neural recording front-end with an integrated real-time compressed sensing unit," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 24–27, 2015, pp. 2996–2999.

- [38] Y. Chen, S. Member, D. Jeon, S. Member, Y. Lee, Y. Kim, S. Member, Z. Foo, I. Lee, S. Member, N. B. Langhals, G. Kruger, H. Oral, O. Berenfeld, Z. Zhang, D. Blaauw, and D. Sylvester, "An injectable 64 nW ECG mixed-signal SoC in 65 nm for arrhythmia monitoring," *IEEE J. Solid-State Circuits*, vol. 50, no. 1, pp. 375–390, 2015.

- [39] C. Liu, S. Chang, G. Huang, and Y. Lin, "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 731–740, 2010.

- [40] P. Harpe, H. Gao, R. van Dommele, E. Cantatore, and A. van Roermund, "A 3 nW signal acquisition IC integrating an amplifier with 2.1 NEF and a 1.5 fJ/conversion-step ADC," in *Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [41] J. Tropp, A. C. Gilbert *et al.*, "Signal recovery from random measurements via orthogonal matching pursuit," *IEEE Trans. Inf. Theory*, vol. 53, no. 12, pp. 4655–4666, 2007.

- [42] F. Chen, A. P. Chandrakasan, and V. M. Stojanovic, "Design and analysis of a hardware-efficient compressed sensing architecture for data compression in wireless sensors," *IEEE J. Solid-State Circuits*, vol. 47, no. 3, pp. 744–756, 2012.

- [43] H. Rhew, J. Jeong, J. Fredenburg, and S. Dodani, "A fully self-contained logarithmic closed-loop deep brain stimulation SoC with wireless telemetry and wireless power management," *IEEE J. Solid-State Circuits*, vol. 49, no. 10, pp. 2213–2227, Oct. 2014.

- [44] Y. Lu, S. Member, and W. Ki, "A 13.56 MHz CMOS active rectifier with switched-offset and compensated biasing for biomedical wireless power transfer systems," *IEEE Trans. Biomed. Circuits Syst.*, vol. 8, no. 3, pp. 334–344, 2014.

- [45] C. J. Deepu, X. Zhang, S. Member, W. Liew, D. Liang, T. Wong, S. Member, and Y. Lian, "An ECG-on-chip with 535 nW/channel integrated lossless data compressor for wireless sensors," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2435–2448, 2014.

- [46] M. Shoaran et al., "Compact Low-power cortical recording architecture for compressive multichannel data acquisition," *IEEE Trans. Biomed. Circuits Syst.*, vol. 8, no. 6, pp. 857–870, 2014.

- [47] D. Gangopadhyay, E. G. Allstot, A. M. R. Dixon, K. Natarajan, S. Gupta, and D. J. Allstot, "Compressed sensing analog front-end for bio-sensor applications," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 426–438, 2014.

- [48] J. Zhang, S. Mitra, Y. Suo, A. Cheng, T. Xiong, F. Michon, M. Welkenhuysen, F. Kloosterman, P. S. Chin, S. Hsiao, T. D. Tran, F. Yazicioglu, and R. Etienne-Cummings, "A closed-loop compressivesensing-based neural recording system," *J. Neural Eng.*, vol. 12, no. 3, 2015.

- [49] W. Biederman, D. J. Yeager, N. Narevsky, S. Member, J. Leverett, R. Neely, J. M. Carmena, S. Member, E. Alon, S. Member, and J. M. Rabaey, "A 4.78 mm2 fully-integrated neuromodulation SoC combining 64 acquisition channels with digital compression and simultaneous dual stimulation," *IEEE J. Solid-State Circuits*, vol. 50, no. 4, pp. 1038–1047, 2015.

Xilin Liu (S'13) received the B.S. degree in electrical engineering from the Harbin Institute of Technology, Harbin, China, and the M.S. degree in electrical engineering from the University of Pennsylvania, Philadelphia, PA, USA in 2011 and 2013, respectively.

Currently, he is working toward the Ph.D. degree at the University of Pennsylvania. His research interests include mixed-signal integrated circuits and systems design for medical applications, brain-machine interface, low-power data converters, and CMOS image sensors.

Mr. Liu received the IEEE Solid-State Circuits Society (SSCS) 2015–2016 Predoctoral Achievement Award. He authored papers that received the Best Paper Award (1st place) of the 2015 Biomedical Circuits and Systems Conference (BioCAS) and the Best Paper Award of the BioCAS Track of the 2014 International Symposium on Circuits and Systems (ISCAS). Also, he was the receipient of the Student-Research Preview Award (honorable mention) of the 2014 IEEE International Solid-State Circuits Conference (ISSCC).

Milin Zhang (S'06–M'11) received the B.S. and M.S. degrees in electronic engineering from Tsinghua University, Beijing, China, in 2004 and 2006, respectively, and the Ph.D. degree from the Electronic and Computer Engineering Department, Hong Kong University of Science and Technology (HKUST), Hong Kong.

After finishing her doctoral studies, she worked as a Postdoctoral Researcher at the University of Pennsylvania, Philadelphia, PA, USA. She joined Tsinghua University as an Assistant Professor in

the Department of Electronic Engineering in 2016. Her research interests include designing of traditional and various non-traditional imaging sensors, such as polarization imaging sensors and focal-plane compressive acquisition image sensors. She is also interested in brain-machine-interface and relative biomedical sensing applications and new sensor designs.

Dr. Zhang has received the Best Paper Award of the BioCAS Track of the 2014 International Symposium on Circuits and Systems (ISCAS), and the Best Paper Award (1st place) of the 2015 Biomedical Circuits and Systems Conference (BioCAS).

**Tao Xiong** (S'14) received the B.S. degree in microelectronics and economics from Peking University, Beijing, China, in 2012, and the M.S.E. degree in electrical and computer engineering in 2014.

Currently, he is working toward the M.S.E. degree in applied math and statistics and the Ph.D. degree in electrical and computer engineering at The Johns Hopkins University, Baltimore, MD, USA. From 2009 to 2012, he was a Research Assistant at National Key Laboratory of Science and Technology on Micro/Nano Fabrication, Beijing, China. His re-

search is focused on the deep learning, compressive sensing, and VLSI design for biomedical applications.

Andrew G. Richardson (M'14) received the B.S.E. degree in biomedical engineering from Case Western Reserve University, Cleveland, OH, USA, in 2000, and the S.M. degree in mechanical engineering and the Ph.D. degree in biomedical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, MA, USA, in 2003 and 2007, respectively.

He was a Postdoctoral Associate at MIT in 2007–2008 and a Senior Fellow at the University of Washington, Seattle, WA, USA, from 2008–2012.

Currently, he is Co-Director of the Translational Neuromodulation Laboratory, Department of Neurosurgery, University of Pennsylvania, Philadelphia, PA, USA. His research interests include neural prostheses for restoring sensory, motor, and memory function.

**Timothy H. Lucas** (M'12) completed his neurosurgery and doctoral training in physiology and biophysics at the University of Washington, Seattle, WA, USA in 2009, followed by subspecialty fellowships at the University of California, San Francisco, San Francisco, CA, USA.

He also served as Senior Registrar in the Atkinson Moreley Wing of St. George's Health Care Trust in London, U.K. As Assistant Professor of Neurosurgery, he directs the Translational Neuromodulation Lab and Co-Directs the Center for Neuroengineering

and Therapeutics at the University of Pennsylvania. Philadelphia, PA, USA. His research focuses on the developing novel neuromodulation strategies to restore function to patients with paralysis. Clinically, he performs craniotomies for tumor and epilepsy in eloquent brain regions using minimally invasive laser and endoscopic techniques.

**Peter S. Chin** (M'12) received the B.S. degree inelectrical engineering, computer science, and mathematics from Duke University, Durham, NC, USA, and the Ph.D. degree in mathematics from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1993 and 1998, respectively.

Currently, he is a Research Professor in the Department of Electrical and Computer Engineering, The Johns Hopkins University (JHU), Baltimore, MD, USA, where he is conducting research in the area of compressive sensing, data fusion, game the-

ory, MHT tracking, quantum-game inspired cyber-security, and cognitive radio. He is a PI for a four-year ONR grant (geometric multi-resolution analysis), applying geometric sparse recovery techniques to high dimensional data with low intrinsic dimension. Prior to joining JHU, he was a Division CTO at SAIC and worked on developing 90 nm technology at LSI Logic Corporation, where he also helped to develop its first embedded DRAM technology jointly with Hitachi Semiconductor in the late 1990s.

**Trac D. Tran** (S'94–M'98–SM'08–F'14) received the B.S. and M.S. degrees from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1993 and 1994, respectively, and the Ph.D. degree from the University of Wisconsin, Madison, WI, USA, in 1998, all in electrical engineering.

In July 1998, he joined the Department of Electrical and Computer Engineering, The Johns Hopkins University, Baltimore, MD, USA, where he currently holds the rank of Professor. In summer 2002, he was an ASEE/ONR Summer Faculty Research Fellow at

the Naval Air Warfare Center Weapons Division, China Lake, CA, USA. He is a Consultant for the U.S. Army Research Laboratory, Adelphi, MD, USA. His research interests are in the field of digital signal processing, particularly in sparse representation, sparse recovery, sampling, multirate systems, filter banks, transforms, wavelets, and their applications in signal analysis, compression, processing, and communications. His pioneering research on integercoefficient transforms and pre-/post-filtering operators has been adopted as critical components of Microsoft Windows Media Video 9 and JPEG XR the latest international still-image compression standard ISO/IEC 29199-2.

Dr. Tran was the Co-Director (with Prof. J. L. Prince) of the 33rd Annual Conference on Information Sciences and Systems (CISS '99), Baltimore, MD, USA, in March 1999. He has served as an Associate Editor of the IEEE TRANSACTIONS ON SIGNAL PROCESSING as well as IEEE TRANSACTIONS ON IMAGE PROCESSING. He was a former Member of the IEEE Technical Committee on Signal Processing Theory and Methods (SPTM TC) and is a current member of the IEEE Image Video and Multidimensional Signal Processing Technical Committee. He received the NSF CAREER Award in 2001, the William H. Huggins Excellence in Teaching Award from The Johns Hopkins University in 2007, and the Capers and Marion McDonald Award for Excellence in Mentoring and Advising in 2009.

**Jan Van der Spiegel** (S'73–M'79–SM'90–F'02) received his M.S. degree in electromechanical engineering and his Ph.D. degree in electrical engineering from the University of Leuven, Belgium, in 1974 and 1979, respectively.

He is a Professor of the Electrical and Systems Engineering, the Director of the Center for Sensor Technologies, and Associate Dean for Professional Program at the School of Engineering and Applied Science at the University of Pennsylvania, Philadelphia, PA, USA. He is the former chair of the

Electrical Engineering and interim chair of the Electrical and Systems Engineering Departments. His primary research interests are in mixed-mode VLSI design, CMOS vision sensors for polarization imaging, biologically based image sensors and sensory information processing systems, and brain-machine interface electronics. He has published over 250 journal and conference papers, and is the co-author of 8 U.S. patents.

Dr. Van der Spiegel received the IEEE Major Educational Innovation Award, and is the recipient of the IEEE Third Millennium Medal, the UPS Foundation Distinguished Education Chair and the Bicentennial Class of 1940 Term Chair. He received the Christian and Mary Lindback Foundation, and the S. Reid Warren Award for Distinguished Teaching, the IBM Young Faculty Development Award and the Presidential Young Investigator Award. He has served on several IEEE program committees (IEDM, ICCD, ISCAS and ISSCC) and was the technical program chair of the 2007 International Solid-State Circuit Conference (ISSCC 2007). He is an Associate Editor of IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, and Section Editor of Electrical and Electronic Engineering of the Journal of Engineering of the IET, and former Editor of the IEEE SSCS Chapters committee from 1998 to 2015. He is currently the President of the IEEE Solid-State Circuits Society. He is a member of Phi Beta Delta and Tau Beta Pi.

**Ralph Etienne-Cummings** (F'13) received the B.S. degree in physics from Lincoln University, Lincoln, PA, USA, in 1988, and the M.S.E.E. and Ph.D. degrees in electrical engineering from the University of Pennsylvania, Philadelphia, PA, USA, in 1991 and 1994, respectively.

Currently, he is a Professor of electrical and computer engineering, and computer science at The Johns Hopkins University, Baltimore, MD, USA. He was the Founding Director of the Institute of Neuromorphic Engineering. He has authored more

than 200 peer-reviewed articles and holds numerous patents.

Dr. Etienne-Cummings has served as Chairman of various IEEE Circuits and Systems (CAS) Technical Committees and was elected as a member of CAS Board of Governors. He also serves on numerous editorial boards. He is a recipient of the NSFs Career and Office of Naval Research Young Investigator Program Awards. He was a Visiting African Fellow at the University of Cape Town, Fulbright Fellowship Grantee, Eminent Visiting Scholar at the University of Western Sydney and has also won numerous publication awards, including the 2012 Most Outstanding Paper of the IEEE TRANSACTION ON NEURAL SYSTEMS AND REHABILITATION ENGINEERING. In addition, he was recently recognized as a Science Maker, an African American history archive.